Arm Processor Design and Prototyping

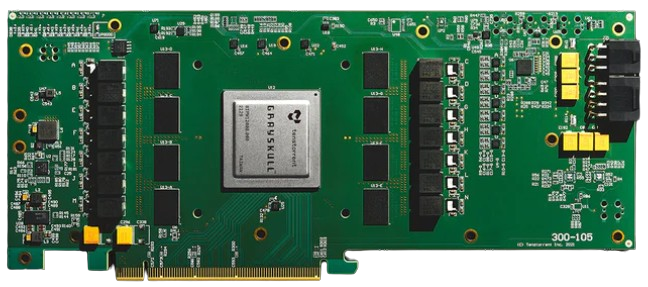

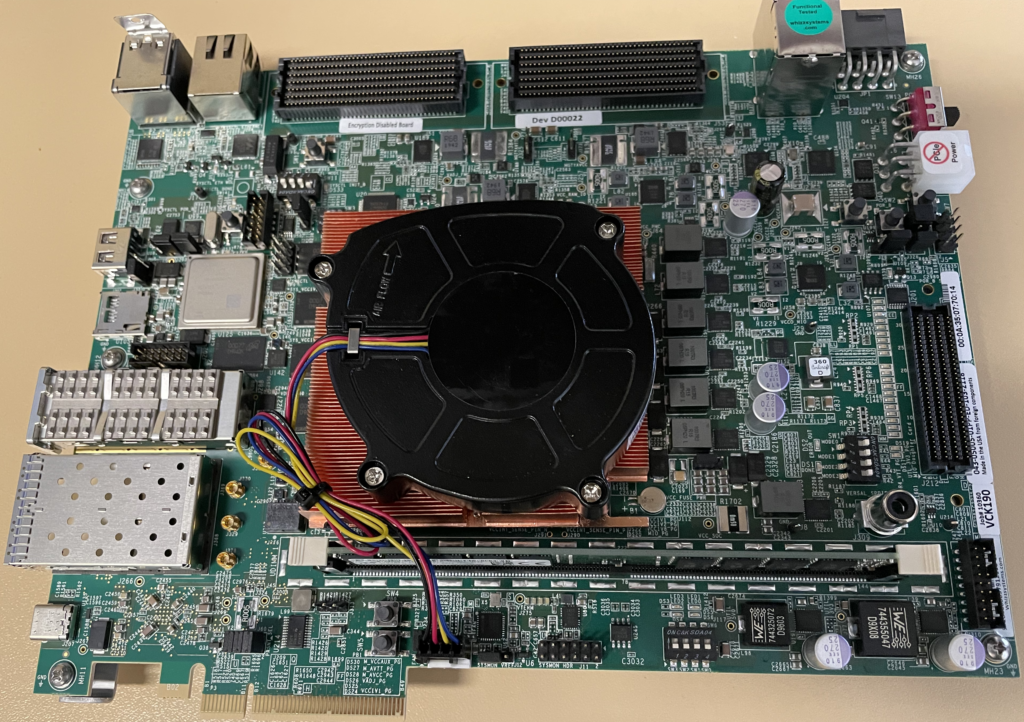

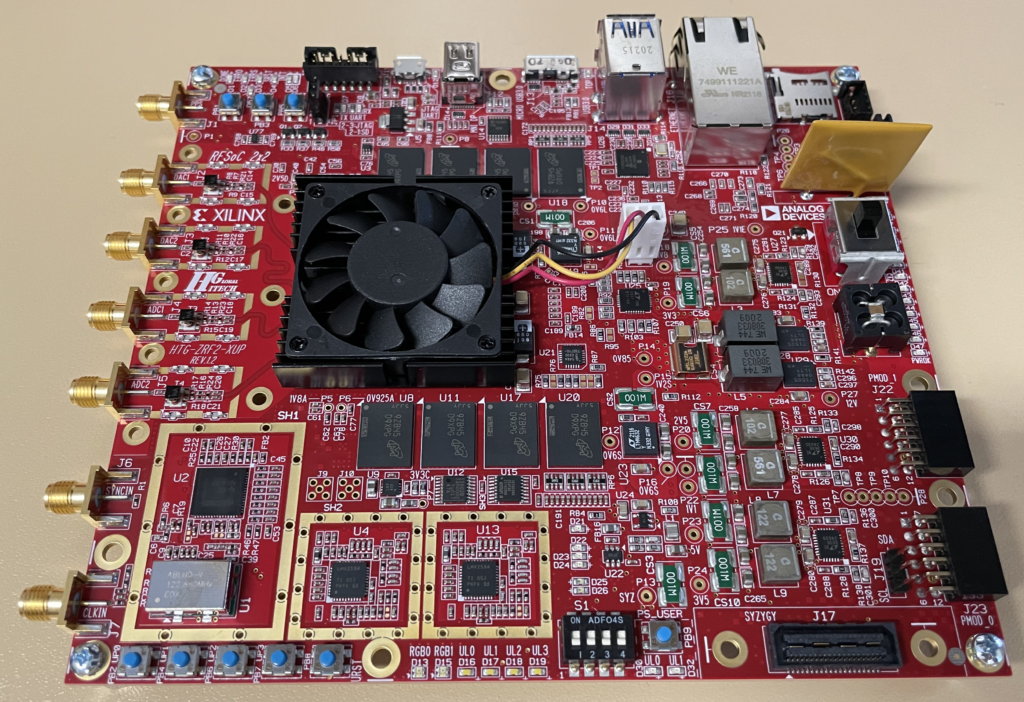

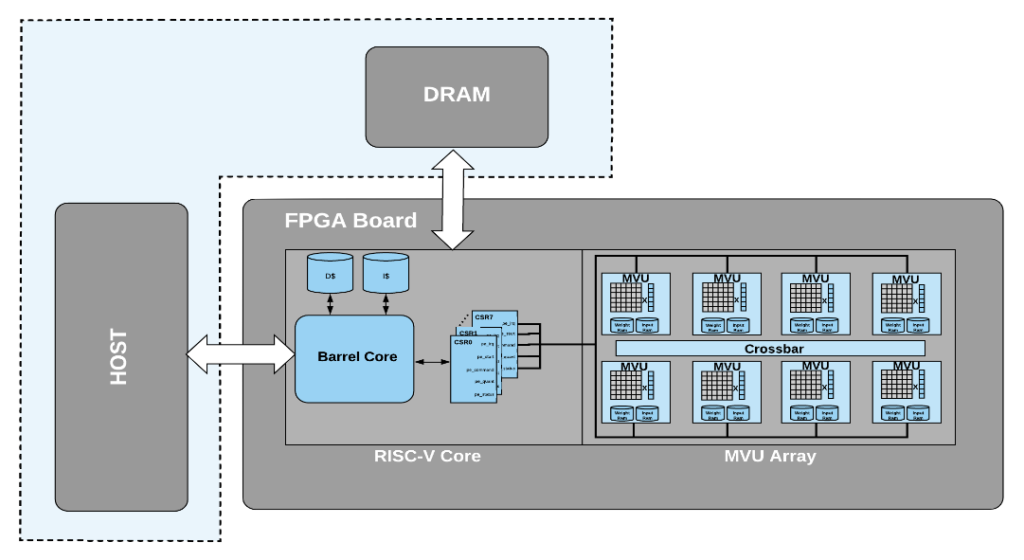

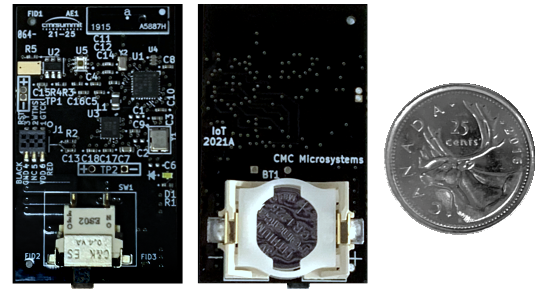

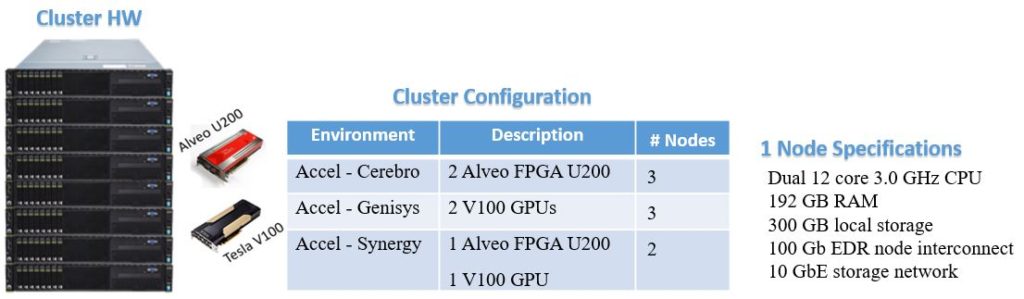

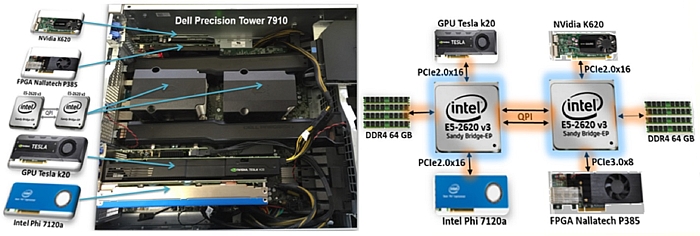

CMC accelerates design and manufacture of Arm-based devices by offering: Industry-standard CAD tools and flows for design, verification, and physical implementation, PCB design, and software development CMC cloud access, pre-configured to ensure quick and easy desktop use FPGA platforms for emulation and validation, early software bring-up and debug Available on-site, through short-term rental or via […]

Arm Processor Design and Prototyping Read More »