Le présent document accompagne la documentation existante sur SDAccel qui est publiée par Xilinx https://www.xilinx.com/products/design-tools/software-zone/sdaccel.html. Le document fournit de l’information sur l’exécution des outils de développement SDAccel dans le nuage informatique de CMC, où vous pouvez utiliser le cadre de travail infonuagique privé pour toutes les tâches de conception, d’émulation et de compilation.

Même si vous connaissez bien les outils SDAccel, lisez la section Premiers pas ci-dessous sur la manière d’exécuter les outils dans le nuage informatique de CMC, et passez en revue le tutoriel Xilinx ci-joint, car les versions de SDx ajoutent de nombreuses améliorations au flux de l’interface graphique de SDAccel.

Premiers pas

- Assurez-vous que votre équipe de recherche dispose de l’accès à la licence Xilinx SDAccel.

- Créez une instance de SDAccel Development Environment (Virtual) (environnement [virtuel] de développement SDAccel) sur le nuage informatique de CMC.

Si vous ne connaissez pas bien l’utilisation du nuage informatique de CMC, consultez le guide de démarrage rapide : utilisation des environnements de conception dans le nuage informatique de CMC. - À partir du terminal dans votre instance du nuage informatique de CMC, configurez les réglages de licence et d’environnement en incluant le script de configuration de SDAccel :

[vowain@vm]$ source /CMC/Xilinx/sdaccel.2018.3.csh

- Exécutez l’interface graphique SDx :

[vowain@vm]$ sdx

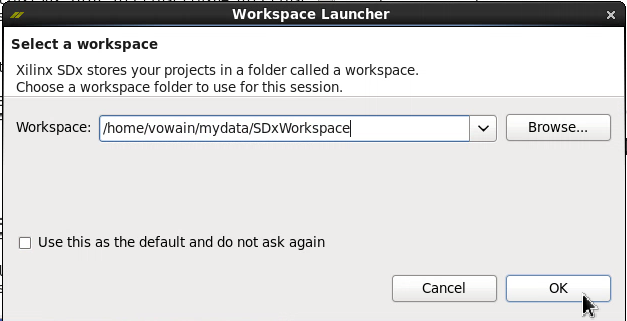

- Au démarrage de SDx, le système vous demandera de préciser l’endroit où se trouve votre espace de travail SDx. L’espace de travail par défaut est votre dossier maison, mais pour profiter de votre stockage persistant dans le nuage informatique de CMC, sélectionnez un dossier dans votre dossier mydata, comme illustré à la figure 1.

Figure 1 : Lanceur d’espace de travail SDx

Utilisation du tutoriel d’environnement Xilinx SDAccel

La présente section a été conçue au moyen du contenu dans les tutoriels SDAccel et les exemples SDAccel publiés par Xilinx sur GitHub.

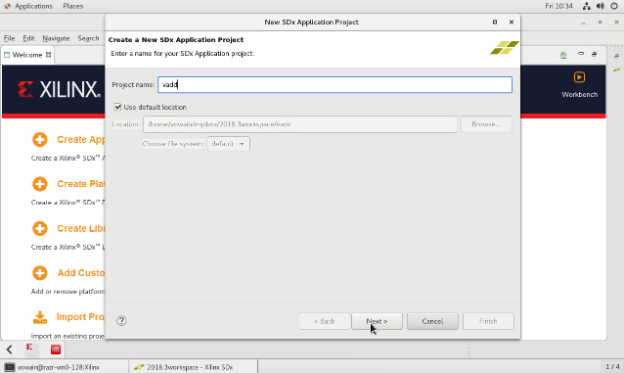

- Dans la fenêtre Welcome (bienvenue), cliquez sur Create Application Project (créer un projet d’application) et nommez votre projet vadd, puis cliquez sur Next (suivant).

Figure 2 : Création d’un projet d’application dans SDx

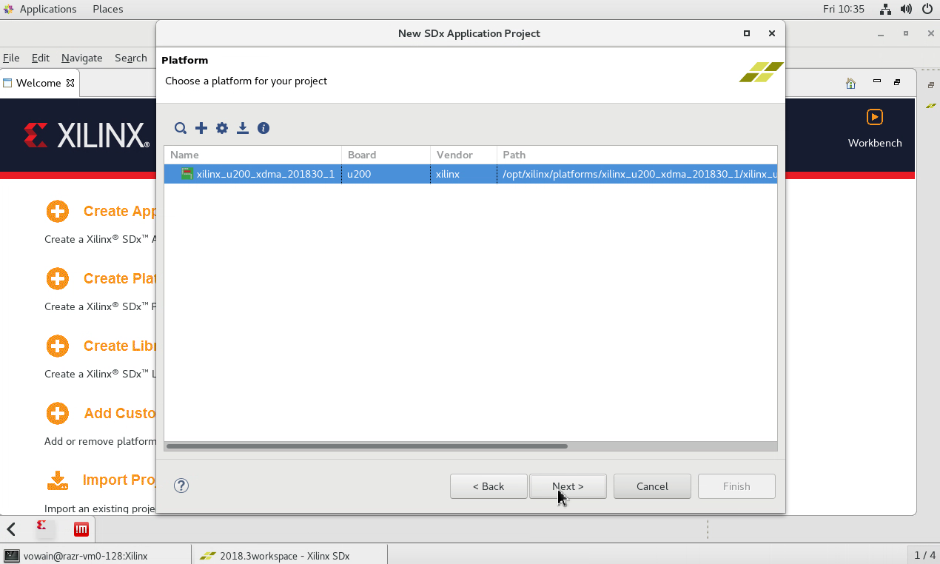

- Si vous suivez ce tutoriel uniquement pour apprendre à utiliser SDAccel, sélectionnez la plateforme par défaut (xilinx_u200_xdma_201830_1), puis cliquez sur Next > (suivant >).

Remarque : Si vous ciblez une matrice FPGA précise dans votre développement, assurez-vous de sélectionner la plateforme appropriée lorsque vous créez votre définition de projet. Si vous ne voyez pas la carte de matrice FPGA que vous souhaitez cibler, contactez le soutien de CMC.

Figure 3 : Sélection de plateforme dans SDx

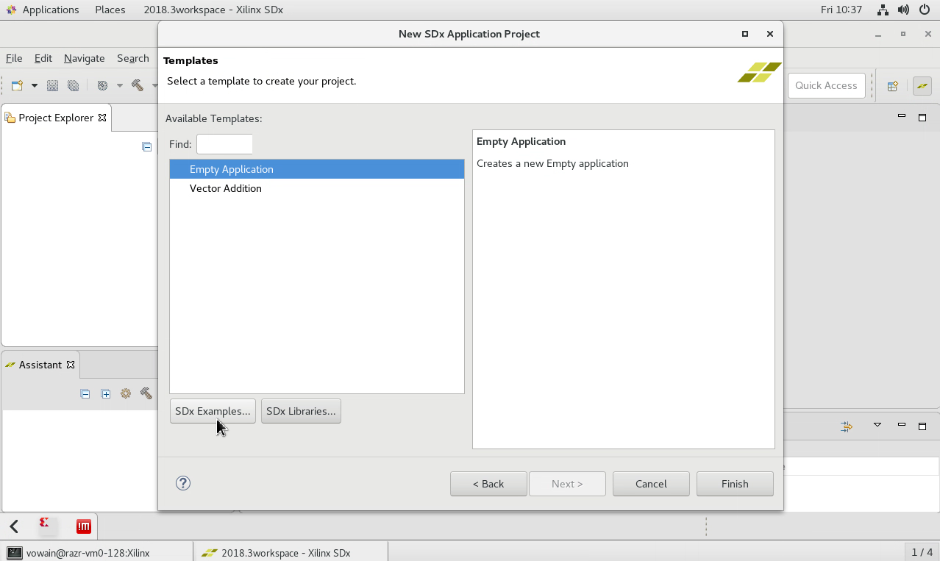

La fenêtre Templates (modèles) apparaît avec les options pour Empty Application (application vide) et Vector Addition (addition de vecteur), comme illustré à la figure 4.

Figure 4 : Boîte de dialogue de modèles dans SDx

- Ce tutoriel utilise les fichiers des exemples sur GitHub. Pour obtenir ces fichiers, cliquez sur le bouton SDx Examples (exemples SDx), comme illustré à la figure 4.

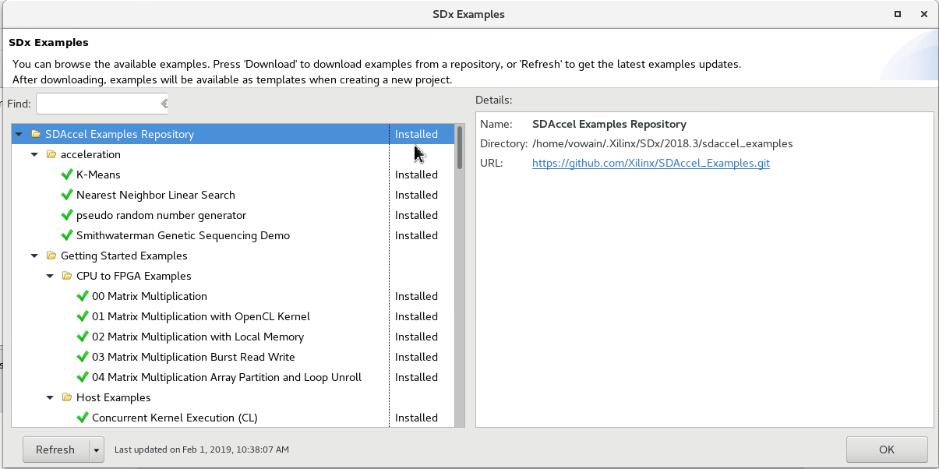

- Dans la fenêtre SDx Examples (exemples SDx), cliquez sur Download (télécharger).

Une longue liste est affichée, comme illustré à la figure 5.

Figure 5 : Exemples SDx

- Pour fermer la fenêtre, cliquez sur OK.

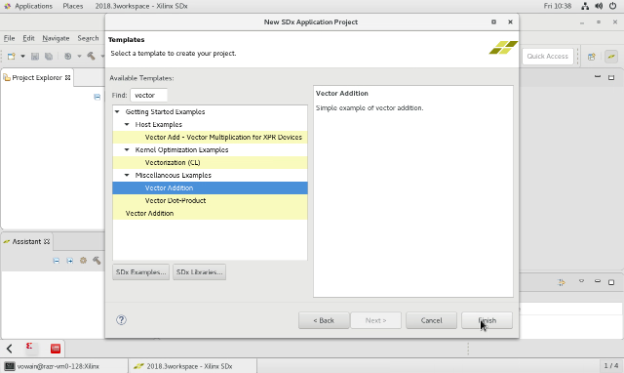

Une longue liste de modèles apparaît dans la fenêtre Templates (modèles). - Dans la zone de texte Find (trouver), entrez vector (vecteur), puis sélectionnez Getting Started Examples -> Miscellaneous Examples -> Vector Addition (exemples de premiers pas -> exemples variés -> addition de vecteur).

REMARQUE : Ne sélectionnez pas Vector Addition (addition de vecteur) situé au bas de la liste et qui est préinstallé avec SDx, comme illustré à la figure 6.

Figure 6 : Modèles SDx alimentés avec exemples téléchargés

- Cliquez sur Finish (terminer).

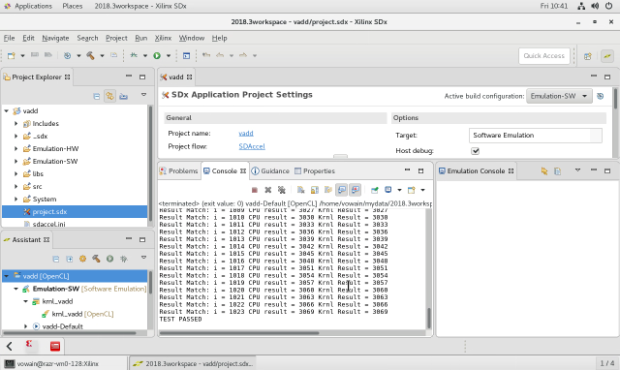

Votre application est maintenant configurée. Par défaut, l’option Active Build Configuration (configuration de compilation active) est réglée à Emulation-SW (émulation logicielle). - Pour compiler l’application et exécuter le logiciel d’émulation, cliquez sur Run (lancer).

Une fois la compilation et l’exécution terminées, la sortie produite par l’application et les mots TEST PASSED (test réussi) apparaissent dans la fenêtre Console, comme illustré à la figure 7.

Figure 7 : Projet d’addition de vecteur dans SDx

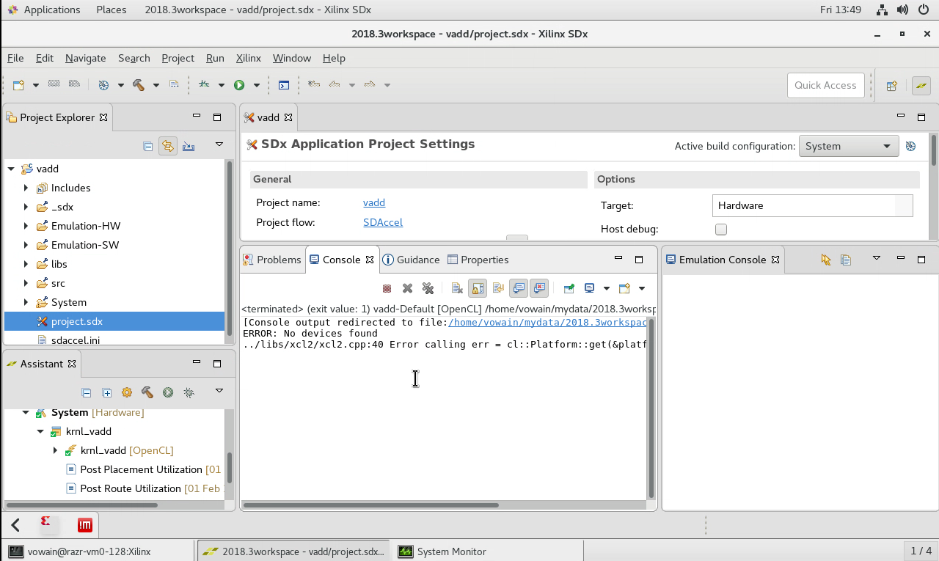

- Pour compiler le fichier binaire qui pourrait être exécuté sur une carte de matrice FPGA physique, remplacez l’option Active build configuration (configuration de compilation active) par System (système), puis cliquez sur Run (lancer).

Cette compilation peut prendre plusieurs heures; de plus, puisqu’il n’y a pas de matrice FPGA physique connectée à l’image du nuage informatique de CMC, le message ERROR: no devices found (erreur : aucun dispositif trouvé) apparaît à la fin du processus, comme illustré à la figure 8.

Figure 8 : Configuration de compilation de système d’application dans SDx

- Même si le fichier binaire compilé ne peut pas être exécuté dans cette image, vous pouvez le transférer vers une machine munie d’une carte de matrice FPGA qui correspond à votre sélection de plateforme, puis l’exécuter. Suivez ces étapes pour trouver le fichier binaire compilé dans le système de fichiers :

- Rendez-vous dans votre dossier d’espace de travail SDx défini à l’étape 5 de la section Premiers pas, puis dans le dossier vadd/System.

- Pour examiner le contenu du dossier, exécutez la commande ls.

- Transférez les fichiers vers votre système local au moyen de SSH :

[vowain@razr-vm0-128 ~]$ cd ~/mydata/2018.3workspace/vadd/System/ [vowain@razr-vm0-128 System]$ ls -lh total 39M -rw-r--r--. 1 vowain vcl 1.7K Feb 1 10:41 guidance.html -rw-r--r--. 1 vowain vcl 207 Feb 1 10:41 guidance.pb drwxr-xr-x. 7 vowain vcl 4.0K Feb 1 13:23 krnl_vadd -rw-r--r--. 1 vowain vcl 2.2K Feb 1 13:23 krnl_vadd.ltx -rw-r--r--. 1 vowain vcl 14K Feb 1 13:23 krnl_vadd.mdb -rw-r--r--. 1 vowain vcl 38M Feb 1 13:23 krnl_vadd.xclbin -rw-r--r--. 1 vowain vcl 5.1K Feb 1 13:23 krnl_vadd.xclbin.info -rw-r--r--. 1 vowain vcl 357 Feb 1 10:42 krnl_vadd.xclbin.sh drwxr-xr-x. 3 vowain vcl 4.0K Feb 1 13:23 libs -rw-r--r--. 1 vowain vcl 4.3K Feb 1 10:41 makefile -rw-r--r--. 1 vowain vcl 64 Feb 1 13:23 sdaccel.ini drwxr-xr-x. 2 vowain vcl 4.0K Feb 1 13:23 src drwxr-xr-x. 2 vowain vcl 4.0K Feb 1 13:24 vadd-Default -rw-r--r--. 1 vowain vcl 120 Feb 1 13:23 vadd-Default.launch.log -rw-r--r--. 1 vowain vcl 30 Feb 1 13:23 vadd-Default.launch.ui.log -rwxr-xr-x. 1 vowain vcl 42K Feb 1 13:23 vadd.exe -rw-r--r--. 1 vowain vcl 17K Feb 1 13:23 vadd_System.build.log -rw-r--r--. 1 vowain vcl 2.3K Feb 1 13:23 vadd_System.build.ui.log

Exécution de vos noyaux sur une carte de matrice FPGA physique

Les étapes ci-dessus peuvent créer les fichiers dont vous avez besoin pour l’exécution sur une carte de matrice FPGA physique. Pour l’exécution réelle, vous devez passer en revue les exigences pour votre environnement et votre plateforme de matrice FPGA dans la documentation en ligne de SDAccel.