# CORE-V: Open Source RISC-V Cores for Industry & Academia

#### Rick O'Connor <u>rickoco@openhwgroup.org</u> T <u>@rickoco</u> T <u>@openhwgroup</u> <u>www.openhwgroup.org</u>

© OpenHW Group

May 2023

- OpenHW Group is a not-for-profit, global organization registered in Canada and Europe. The OpenHW ecosystem is driven by members (corporate & academic) and individual contributors where HW and SW designers collaborate in developing open-source cores, related IP, tools and SW such as the CORE-V Family of open-source RISC-V processors

- International footprint with developers in North America, Europe and Asia

- Providing an infrastructure for hosting high quality open-source HW developments in line with industry best practices

- Strong support from industry, academia and individual contributors worldwide

Смс : CSem ETH zürich

ÉCOLE DE TECHNOLOG SUPÉRIEURE

ÉTS

BSC Barcelona Supercomputing Center Centro Nacional de Supercomputación

Cez

# Working Groups & Task Groups

- Board of Directors approves elected Chairs of Working Groups and has final approval of working group recommendations

- Technical Working Group

- Cores Task Group

- Verification Task Group

- SW Task Group

- HW Task Group

- Marketing Working Group

- University Outreach Task Group

- OpenHW Asia Working Group

- OpenHW Europe Working Group

- Together with internal OpenHW Group engineering staff, member company development engineers (FTEs / ACs) establish and execute <u>OpenHW Group projects</u>

- 20+ active projects across CORE-V RTL, Verification, GCC / LLVM, IDE, RTOS, FPGA, SoC, etc. with more projects in the pipeline

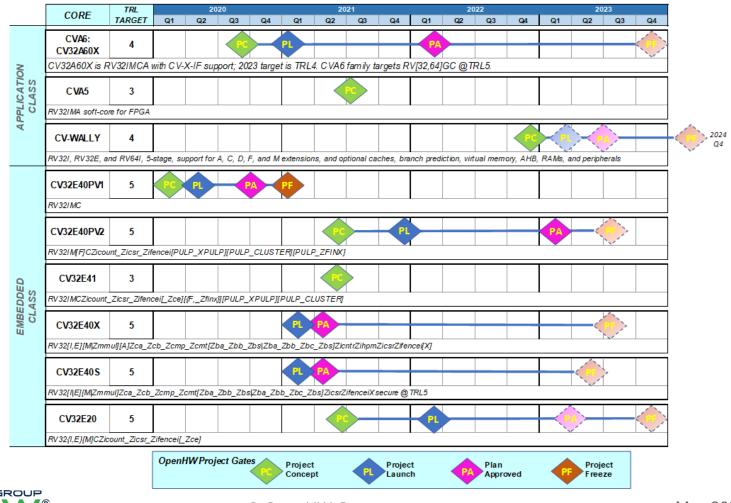

### OpenHW Cores Task Group

- Chair: Arjan Bink, Silicon Laboratories

- Vice-Chair: Jérôme Quévremont, Thales Research & Technology THALES

- develop feature and functionality roadmap and the open-source IP for the cores within the OpenHW Group such as the CORE-V Family of open-source RISC-V processors.

- Initial contribution of open-source RISC-V cores from <u>ETH Zurich PULP Platform</u> and the OpenHW Group is the <u>official committer for these repositories</u> ETH zürich I and I a

| ( <b>RI5CY)</b> 4- | 32bit /<br>4-stage   | A family of 4-stage cores that implement, RV32IMFCXpulp, optional 32-bit FPU, instruction set extensions for DSP operations including HW loops, SIMD extensions, bit manipulation and post-increment instructions.                                                                                                                                              |

|--------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CVA6</b> 32 8   |                      |                                                                                                                                                                                                                                                                                                                                                                 |

|                    | & 64bit /<br>6-stage | A family of 6-stage, single issue, in-order CPU cores implementing RV64GC extensions<br>with three privilege levels M, S, U to fully support a Unix-like (Linux, BSD, etc.)<br>operating system. The cores have configurable size, separate TLBs, a HW PTW and<br>branch-prediction (branch target buffer, branch history table and a return address<br>stack). |

SILICON LABS

#### OpenHW GitHub <a href="https://github.com/openhwgroup">https://github.com/openhwgroup</a>

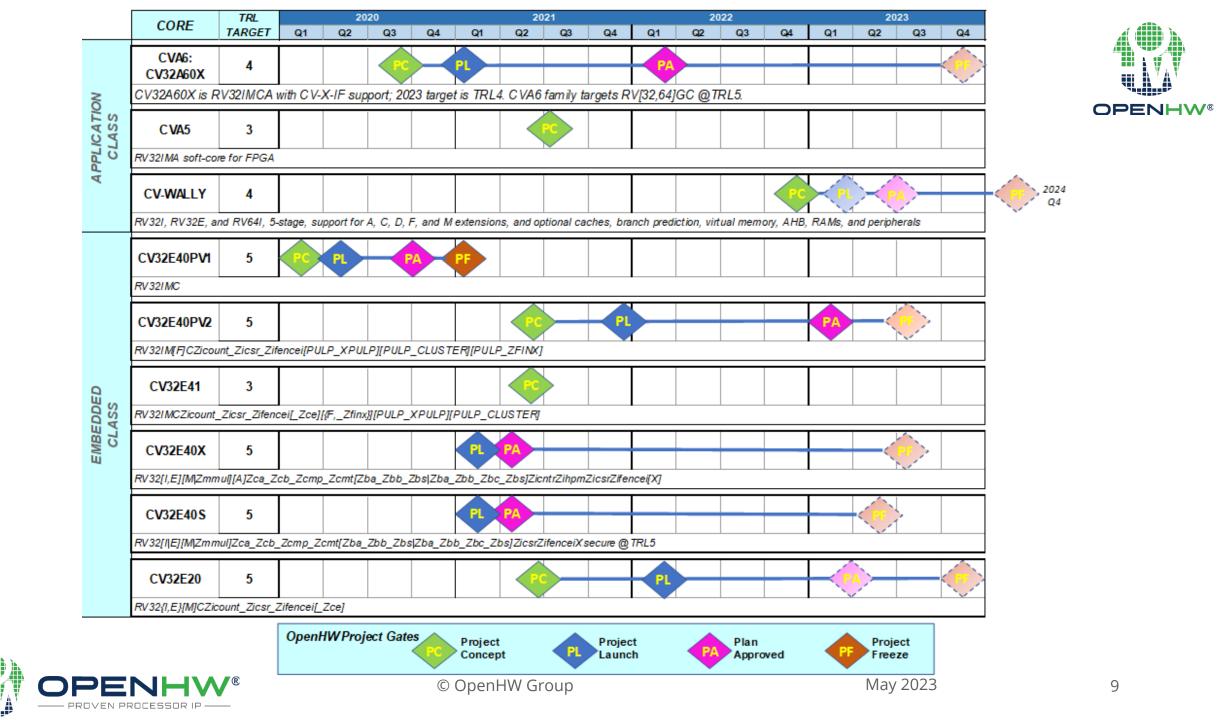

# CVE4 Family CV32E40P

data interface

- 4-stage, in-order, singleissue

- RV32IM[F]CZicount\_Zicsr\_Zi fencei

[PULP\_XPULP][PULP\_CLUST ER][PULP\_ZFINX]

- M-mode, CLINT, OBI

- 'RTL Freeze' achieved

- RV32IMC extensions verified

- Interrupts and Debug

© OpenHW Group

10

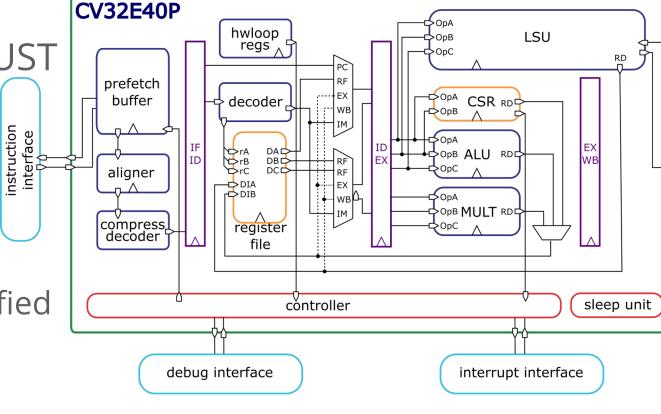

## CVA6 Family

- 6-stage, in-order, single-issue

- RV{32|64}IMAC[FD] Zicsr

- M/S/U-mode, CLINT, AXI

- Flexible application core

- Linux-compatible thanks to MMU

- 32 or 64 bit (CV32A6, CV64A6) from same RTL (64b from ETH, 32b from Thales)

- L1 caches

#### HW Task Group

- Chair: Hugh Pollitt-Smith, CMC Microsystems

- Vice-Chair: Tim Saxe, QuickLogic

- define, develop and support SoC and FPGA based evaluation / development platforms for the cores and IP developed within the OpenHW Group.

QuickLogic®

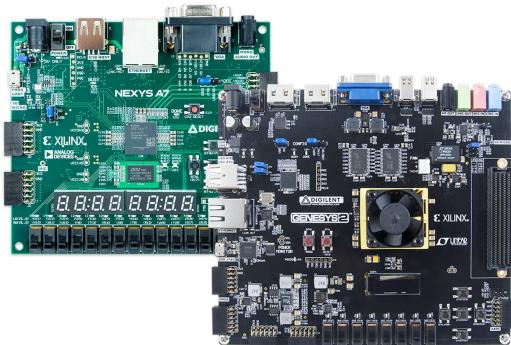

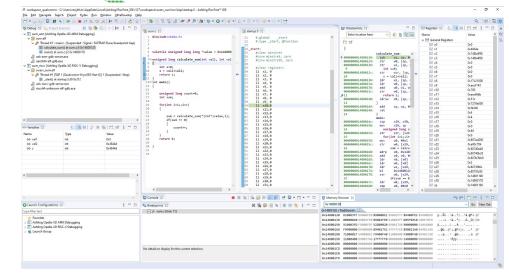

CORE-V projects leverage Digilent NexysA7 & Genesys2 FPGA boards for soft-core bring up for both CVE4 and CVA6 Families

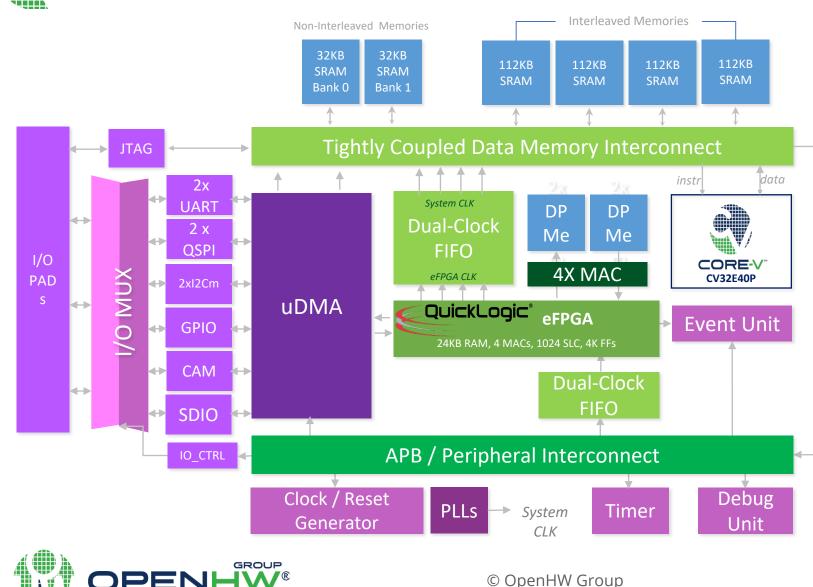

# CORE-V® MCU Tapeout 1st half 2023

- Real Time Operating System (e.g. FreeRTOS) capable

~300+MHz CV32E4 MCU

- Embedded FPGA fabric with hardware accelerators from QuickLogic

- Multiple low power peripheral interfaces (SPI, GPIO, I2C, HyperRAM, CAMIF, etc) for interfacing with sensors, displays, and connectivity modules

• Built in 22FDX with

May 2023

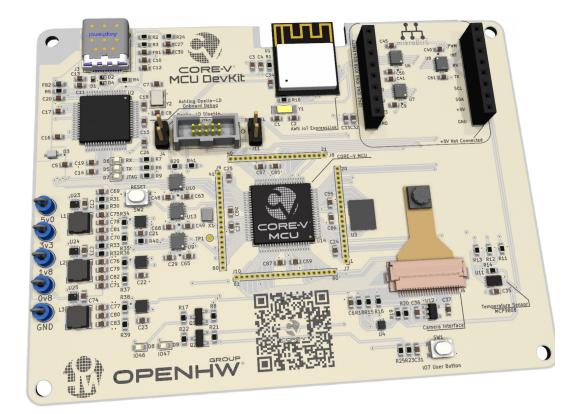

**OpenHW CORE-V DevKits**

- CORE-V MCU SoC

- CV32E40P processor core

- Quicklogic ArticPro eFPGA

- Global Foundries 22FDX

- Ashling Opella-LD onboard JTAG debug module

- USB-C for terminal and onboard debug access

- JTAG connector for external debug access

- Espressif AWS IoT ExpressLink Module for AWS IoT cloud interconnect

- mikroBUS onboard socket, allowing access to a vast range of mikroBUS modules

- 40 pin expansion header

- I2C temperature sensor

- Early Access CORE-V MCU DevKits can be reserved on the <u>GroupGets campaign page</u> (quantities are limited)

#### CVA6 – software support

- OpenSBI

- U-boot

- Linux

- FreeRTOS

- Yocto

- RISC-V standard toolchain (gcc, gdb, openOCD)

- Eclipse IDE

$\tau o$

**U-Boot**

#### CVA6 – dual core SMP Linux on Genesys2

|            |          | masgia@masgia-Inspiron-5579: ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - 🗆 😣 |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Open Piton | <image/> | <pre>masgla@masgla-Inspiron-5579:-  File Edit View Search Terminal Help  L2.508437] fff8c2c080.uart: ttyS9 at MND 0xfff8c2c080 (irq = 1, base_baud = 4106087) is a 10550 (1.5.408457] fff8c2c080.uart: ttyS9 at MND 0xfff8c2c080 (irq = 1, base_baud = 4166687) is a 10550 (1.5.40857) prints: console [ttyS0] enabled (1.5.40857) prints: div1.0 Apr 26, 2019 (1.5.40857) prints: div1.0 Apr 26, 2019 (1.5.40857) prints: div1.0 Apr 26, 2019 (1.5.40857) prints: prints: div10n sd2 (1.6.20807) prints: prints: div10n sd2 (1.6.308381) libphy: Fixed MDIO Bus: probed (1.6.318435) libphy: Fixed MDIO Bus: probed (1.6.345813) libphy: Xilinx Emaclite MDIO: probed (1.6.345813) libphy: Xilinx Emaclite MDIO: probed (1.6.355367) Xilinx emaclite fff0d00000.ethernet: Device Tree Probing (1.6.355367) Xilinx emaclite fff0d00000.ethernet: MC address is now 00:18:3e:02:e3:e5 (1.6.355367) Xilinx emaclite fff0d00000.ethernet: Xilinx Emaclite at 0x(ptrval) mapped to 0x(ptr (1.6.45581) libphy: Xilinx Emaclite MDIO: probed (1.6.35537) Xilinx emaclite fff0d00000.ethernet: Xilinx Emaclite at 0x(ptrval) mapped to 0x(ptr (1.6.455841) libphy: Xilinx Emaclite MDIO: probed (1.6.345813) libphy: Xilinx Emaclite ff0d00000.ethernet: Xilinx Emaclite at 0x(ptrval) mapped to 0x(ptr (1.6.455841) libphy: Size 0 eFinanced' Host Controller (EHCI) Driver (1.6.455841) usbcroe: registered new interface driver usbhid (1.6.475812) NET: Registered protocol family 10 (1.6.475812) NET: Registered protocol family 10 (1.6.475812) NET: Registered protocol family 10 (1.6.476812) NET: Registered protocol family 10 (1.6.476812) NET: Registered protocol family 17 (1.6.561097) Key type dns_resolver registered (1</pre>                | val2  |

|            |          | <pre>[ 18.860994] This architecture does not have kernel memory protection. [ 18.874036] Run /init as init process [ 18.874036] Run /init as init process Starting logging: OK Initializing random number generator [ 21.273658] random: dd: uninitialized urandom read (512 bytes read) [ 21.273658] random: dd: uninitialized urandom read (512 bytes read) done. Starting rpcbind: OK [ 22.539276] random: ssh-keygen: uninitialized urandom read (32 bytes read) [ 22.539276] random: ssh-keygen: uninitialized urandom read (32 bytes read) [ 22.539276] random: ssh-keygen: uninitialized urandom read (32 bytes read) [ 22.799293] random: ssh-keygen: uninitialized urandom read (32 bytes read) [ 22.799293] random: ssh-keygen: uninitialized urandom read (32 bytes read) [ 22.799293] random: ssh-keygen: uninitialized urandom read (32 bytes read) [ C2.799293] random: ssh-keygen: uninitialized urandom read (32 bytes read) [ C32.bytes read) [ C32.bytes read] [ C32.bytes read]</pre> | 1     |

| GROUP      |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

© OpenHW Group

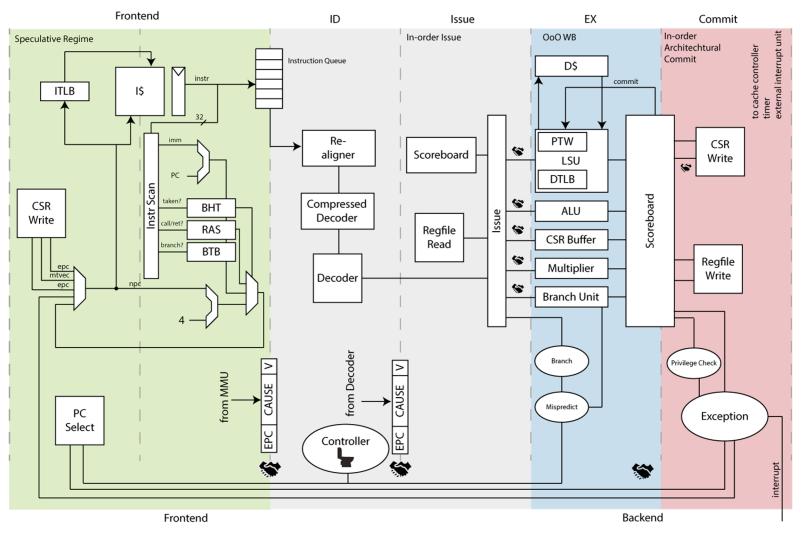

#### CVA6 – 16 core cluster on Stratix10

|                                                                                                                                                                                                                                                                      |                                                                                              | masgia@masgia-Inspiror | -5579: ~ | _ 0 ( |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------|----------|-------|

| File Edit View Se                                                                                                                                                                                                                                                    | arch Terminal Help                                                                           |                        |          |       |

| OpenHW CORE-V (                                                                                                                                                                                                                                                      |                                                                                              |                        |          |       |

| FPGA Board:<br>Build Date:                                                                                                                                                                                                                                           | s10gx<br>Dec 12 2022 08:13:16                                                                |                        |          |       |

| #X-Tiles:<br>#Y-Tiles:<br>#Cores:<br>Core Freq:<br>Network:<br>DRAM Size:                                                                                                                                                                                            | 4<br>4<br>16<br>50 MHz<br>2dmesh config<br>1024 MB                                           |                        |          |       |

| L1I Size / Assoc:<br>L1D Size / Assoc:<br>L15 Size / Assoc:<br>L2 Size / Assoc:                                                                                                                                                                                      | 8 kB / 4<br>8 kB / 4                                                                         |                        |          |       |

| Hello from CVA6 II<br>Hello from CVA6 II | 01<br>02<br>03<br>04<br>05<br>06<br>06<br>07<br>08<br>09<br>10<br>11<br>12<br>12<br>13<br>14 |                        |          |       |

|                                                                                                                                                                                                                                                                      | 115200 8N1   NOR   Minico                                                                    |                        |          |       |

© OpenHW Group

# OpenHW Accelerate 1<sup>st</sup> Project

- 1<sup>st</sup> OpenHW Accelerate Co-Funded Project CORE-V CV-VEC: RISC-V Vector Processor for Highthroughput Multidimensional Sensor Data Processing & Machine Learning Acceleration at the Edge

- Gord Harling, Hugh Politt-Smith, CMC (Industry Sponsor)

- Frank Gürkaynak, Matheus Cavalcante, Matteo Perotti, ETH Zürich

- Yvon Savaria, Nizar El Zarif, Hossein Askari Hemmat, Yoan Fournier, Elisabeth Humblet, Polytechnique Montréal

- Jonathan Balkind, Ci-Chian Lu, UC Santa Barbara

**ETH** zürich

Mitacs

POLYTECHNIQUE

MONTRÉAL

WORLD-CLASS ENGINEERING

ETH zürich UC SANTA BARBARA

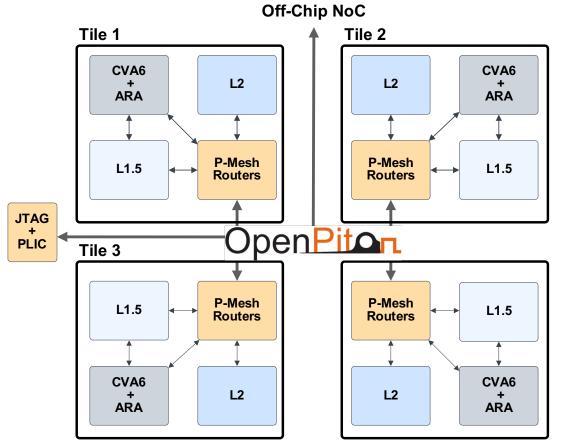

#### **CORE-V Polara Quad core Architecture**

- Adding latest CVVEC (Ara) with sub-byte computation support into OpenPiton.

- Adding latest CVA6 with accelerator interface support into OpenPiton.

- Developing OpenPiton to AXI interface to connect OpenPiton NOC to CVVEC.

ETH zürich UC SANTA BARBARA

### **CORE-V Polara ASIC design**

| Name                                        |                              |         | CORE-V Polara       |  |  |  |

|---------------------------------------------|------------------------------|---------|---------------------|--|--|--|

| Technology                                  | GLOBALFOUNDRIES 22FDX FD-SOI |         |                     |  |  |  |

| Package                                     |                              |         | CPGA208             |  |  |  |

| Target frequency <sup>1</sup>               |                              |         | $> 1 \mathrm{~GHz}$ |  |  |  |

| $Power^2$                                   |                              |         | < 1.25  W           |  |  |  |

| Width                                       |                              |         | -<br>3 mm           |  |  |  |

| Height                                      |                              |         | 3  mm               |  |  |  |

| Area                                        |                              |         | $9 \text{ mm}^2$    |  |  |  |

| I/Os                                        |                              |         |                     |  |  |  |

| $\mathbf{Type}$                             | Inputs                       | Outputs | Total               |  |  |  |

| Power                                       | 112                          | 0       | 112                 |  |  |  |

| VDDC                                        | 28                           | 0       | 28                  |  |  |  |

| VDDIO                                       | 28                           | 0       | 28                  |  |  |  |

| VSSC                                        | 28                           | 0       | 28                  |  |  |  |

| VSSIO                                       | 28                           | 0       | 28                  |  |  |  |

| Off-Chip Interface (OCI)                    | 46                           | 39      | 85                  |  |  |  |

| Reset                                       | 1                            | 0       | 1                   |  |  |  |

| $FLL \ {\ensuremath{\mathfrak{E}}} \ Clock$ | 4                            | 1       | 5                   |  |  |  |

| JTAG                                        | 4                            | 1       | 5                   |  |  |  |

| Chip bridge (data)                          | 37                           | 37      | 74                  |  |  |  |

| Total                                       | 158                          | 39      | 197                 |  |  |  |

- CORE-V Polara tape-out planned for this year

- GF22FDX

- 3x3 mm die

• Quad core SoC with 4 instances of CVA6+CVVEC at 4 lanes each

- OpenHW Group & CORE-V Family of open-source RISC-V cores for use in high-volume production SoCs

- Visit <u>www.openhwgroup.org</u> for community information

- Visit OpenHW GitHub <u>https://github.com/openhwgroup</u> for projects

- Learn more at <u>OpenHW TV</u>

• Follow us on Twitter <u>@openhwgroup</u> & <u>LinkedIn OpenHW Group</u>