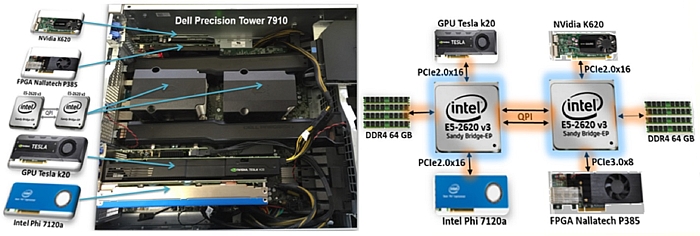

HPP Accelerators

| Accelerator | Features | Host Interface | Compute Performance | Power |

|---|---|---|---|---|

| Nallatech 385 | Altera Stratix VMemory: 2 banks of 4 GB | PCIe 3.0 x 8 | Unavailable | Typical application ≤ 25 W |

| Tesla K20 | 2496 CUDA coresMemory: 5 GB at 208 GB/s | PCIe 2.0 x 16 | 3.52 TFLOPS (single precision)1.17 TFLOPS (double precision) | 225 W |

| Xeon Phi 7120a | 61 cores, 1.33 GHzMemory: 16 GB at 352 GB/s | PCIe 2.0 x 16 | Peak double precision 1.003 TFLOPS | 300 W |

HPP Software Stack and Tools

| GPU Tesla K20 | CUDA, C, CUDA C++, DirectCompute 5.0OpenCL, Java, Python, Fortran |

|---|---|

| Nallatech FPGA 385 | Altera: Quartus, SDK for OpenCL |

| Xeon Phi 7120a | Intel Parallel Studio XE Intel C++/C/Fortran compliers, Intel Math Kernel LibraryDebuggers, Performance and Correctness Analysis ToolsOpenMP, MPI, OFED messaging infrastructure (Linux only), OpenCLProgramming Models: Offload, Native and mixed Offload + Native |

Benefits

- Customizability: Select the right mixt of accelerators for your application

- Greater flexibility for HW/SW exploration

- Scalability: Create one node and scale up by adding more nodes

- Fast automated setup and configuration

- Faster path to commercialization

- Technical support and training from CMC Microsystems

Applications

- Software IPs and applications targeting heterogeneous parallel systems (e.g., imaging, video, and next-generation immersive applications such as computational photography and augmented reality)

- Software stack including : parallel programming models, Compilers, Middleware, Runtime, Drivers and OSes

- Hardware/Software exploration

- Debug and trace of applications running on a heterogeneous parallel system

Services

- Online community forum

- Technical support and training from CMC Microsystems

- Documentation including design handbooks, application notes and design methodologies

Resources

Webinars

- Introduction to HPP Webinar

- Introduction to HPP Webinar Slides

- HPP Webinar #2: Programming Models, Performance and Power Profiling for the Heterogeneous Parallel Platform (HPP)

- HPP Webinar #2 Slides

- HPP Webinar #3: Computer Vision Using OpenCV/OpenCL Targeting the HPP

- HPP Webinar #3 Slides

- Deep Learning TensorFlow on the HPP-Heterogeneous Processing Platform